Beyond the GPU: The 2026 CPU Bottleneck No One Is Pricing In

As AI shifts from $/Token to $/Task, tomorrow’s agentic and robotic workloads are turning CPUs into the new constraint. We map the demand shift and the CPU supply chain to unlock the opportunities.

A quick vibe check on where the market is heading: NVIDIA ($NVDA) is no longer just selling “the GPU.” With the Rubin platform, NVIDIA is now shipping the matching CPU (Vera) and crucially positioning it as infrastructure that can show up as standalone control-plane capacity inside modern AI data centers. And CoreWeave ($CRWV) is among the first public examples waving the flag here: they’ve announced they’ll be an early adopter of NVIDIA’s CPU + storage platforms in their fleet.

This means $NVDA has officially entered the CPU room with $INTC and $AMD.

That matters because the market is still pricing “intelligence” like it’s a single forward pass: How many tokens per second can you generate? That was the right KPI for chatbots. It’s the wrong KPI for agents.

What’s changing in 2026 isn’t that models suddenly got mystical. It’s that we’re moving from Generation (GPUs) to Orchestration (CPUs + networking + memory + isolation)—and the bottleneck shifts from how fast the model can speak to how much infrastructure you can afford to keep thinking running.

FPX AI CPU Marketplace

If you’re looking to buy or rent CPU-only servers for orchestration, rollouts, tooling,

or control-plane capacity, reach out to us.

We can source and deliver validated configs with known lead times.

Explore : https://marketplace.fpx.world/cpus-for-sale

Full marketplace : https://marketplace.fpx.world/

Tokens/sec was a chatbot metric. Agents live and die by $/Completed Task.

In the chatbot world, the unit of work is simple:

A user prompt → one completion → done.

That’s why tokens/sec and $/token felt like gravity.

Agents break that mental model. The new unit of work is:

A user goal → a loop that plans → acts → checks → retries → logs → learns → repeats.

So the KPI flips. The KPI becomes:

cost per successful task (not cost per token).

Because in the agent world, the “answer” is often the smallest part of the job. The job is the messy reality around the answer: tool calls, network requests, sandboxes, retries, verification passes, state updates, and audit trails.

This is the part most “GPU = AI” narratives quietly skip. GPUs generate proposals. CPUs operationalize them.

The passive vs. the recursive: why the “Idle Tax” turns into a Work Tax

Traditional software is responsive. It waits. It wakes up when a human clicks something.

Agentic software is recursive. It lives inside a loop.

A chatbot is idle when you are.

An agent is not.

Even “boring” enterprise agent behavior is basically continuous orchestration:

It polls inboxes, watches dashboards, tails logs, checks regressions, reconciles mismatches, retries flaky jobs, gathers evidence, runs experiments to increase certainty, and escalates only when confidence drops below a threshold.

That’s why the Idle Tax becomes a Work Tax: the system consumes cycles while nobody is watching because the whole point is that it keeps going.

And that continuous “going” is overwhelmingly CPU + I/O + network + safety, not token generation.

Here’s the uncomfortable measurement: tool processing can dominate end‑to‑end latency.

If you want one empirical datapoint that snaps this into focus, it’s this: profiling work on agentic frameworks shows that CPU-side tool processing can consume the majority of total latency in representative agent workloads—in one study, up to ~90.6% of total latency—and can also be a large chunk of dynamic energy at scale.

Another 2026 system study looking at agentic inference traces from a large cloud provider finds tool execution dominates tail latency—roughly 30–80% in their measured “first-token response” path, with individual tool calls sometimes exceeding LLM prefill time.

That’s the hidden tax: once you move from “talk” to “do,” your wall-clock time gets eaten by everything around the model.

“But won’t the GPU run the agent loop?” Why GPUs still hate branching, waiting, and bureaucracy.

A skeptical hardware architect will (correctly) point out that GPUs are getting more flexible: CUDA graphs, more conditional logic, tighter scheduling, better kernels—sure.

But here’s the fundamental problem: GPUs are throughput machines. They’re built to do the same kind of work across a lot of lanes in parallel.

Agent loops are the opposite:

They’re full of if/else branches, divergent code paths, serialization points, and—most importantly—waiting (on APIs, on web pages, on filesystem I/O, on permission checks, on sandbox spin‑up).

This is where the economics get brutal:

Using a $30,000 GPU to wait for a weird third‑party API response is capital inefficiency bordering on comedy.

So even if you can run more control flow on the GPU, you generally shouldn’t—because serialization is the enemy of parallelism. When your agent is blocked on an HTTP “200 OK,” you’re effectively stalling thousands of CUDA cores.

That’s why the CPU’s role doesn’t vanish. It evolves into something more specific:

The GPU stays the throughput engine. The CPU becomes the latency absorber.

A selfish FPX CPU Marketplace plug

This is where procurement stops looking like “pick a CPU brand” and starts looking like systems design. If the agent loop is dominated by branching, waiting, tool calls, and I/O, then what matters is the throughput envelope around the model: single-thread responsiveness, memory bandwidth, NVMe IOPS, and NIC capacity—plus the ability to scale rollout workers without wasting expensive compute. That’s why FPX’s CPU marketplace is organized by workload roles, not marketing names: rollout nodes, control-plane nodes, and high-memory sim nodes, with clear spec bands (CPU class, RAM tier, NVMe layout, NIC tier) and lead-time-aware alternates. If you’re looking to buy or rent CPU-only servers, reach out—and if you need GPU, storage, or networking too, the broader FPX HPC marketplace covers those builds as well.

The hardware reality check: what “orchestration” looks like in a Rubin‑era rack

It’s worth grounding this in what $NVDA is literally selling.

NVIDIA’s Vera Rubin NVL72 is positioned as a rack-scale “AI factory” building block: 72 Rubin GPUs + 36 Vera CPUs, tied together with NVLink and a lot of networking hardware.

And the specs read like a confession that orchestration is now first-class:

Vera CPU: 88 custom Arm cores (“Olympus”), designed for orchestration workloads, with up to 1.5TB of LPDDR5X per CPU via SOCAMM, and coherent CPU↔GPU communication via NVLink‑C2C.

The rack includes BlueField‑4 DPUs and ConnectX‑9 SuperNICs—because the “agent loop” isn’t just compute; it’s east‑west traffic, security enforcement, and data movement.

NVIDIA markets the whole thing as a platform for “AI reasoning,” not just training/inference throughput—i.e., long-horizon loops that benefit from coherent orchestration and massive memory plumbing.

And here’s the nuance that makes the strategic tension interesting: even while pushing Vera, NVIDIA’s own DGX Rubin NVL8 spec still lists dual Intel Xeon 6776P host CPUs—a reminder that the transition from “general purpose host” to “specialized control plane” is real, but not instantaneous.

So yes, $NVDA is pushing vertical integration. But even $NVDA is living in a mixed world.

The examples get sharper when you tie them to hardware, not software vibes

A lot of agent talk stays abstract. The easiest way to make this real is to take three common agent loops and translate them into “what the silicon is actually doing.”

DevOps / remediation agents (the “commit → fail → fix → retry” loop) aren’t compute-heavy in the GPU sense; they’re reality-heavy. They clone repos, install dependencies, run unit tests, parse stack traces, spin sandboxes, and repeat. Most of that is CPU time (and disk/network time). The GPU proposes an edit; the CPU pays the bill for testing it.

Security/SOC triage agents spend their lives in parsing, filtering, correlating, and routing. That’s branchy text processing and huge volumes of I/O. Again: the GPU helps you propose the remediation playbook; the CPU does the grunt work of log wrangling, SIEM queries, and rule-engine execution.

Procurement / market intel agents are basically schedulers with opinions. Scraping supplier sites, normalizing messy HTML/PDFs, matching SKUs, diffing changes, and retrying flaky endpoints is less “matrix multiplication” and more “branch prediction + single-thread performance + networking.”

So when you say “web scraping is not a GPU problem,” you can make it more precise:

It’s often a branch-prediction and single-thread latency problem. Parsing ugly real-world documents rewards high-frequency cores, strong caches, and fast I/O—not bigger tensor cores.

The “Hidden Thinking” tax: test‑time compute turns inference into search, and search turns memory into the battlefield

We’re entering test-time compute economics. Modern reasoning stacks increasingly behave like search:

They branch, sample, verify, score, and select—especially as you push toward higher reliability.

That changes the shape of workloads:

Inference stops being “one pass,” and starts being “a tree of attempts.”

Even if the GPU does the heavy math, the CPU increasingly becomes the thing that:

Schedules branches, manages retries, routes tool calls, stores intermediate state, enforces budgets/timeouts, merges candidate solutions, and logs traces for improvement.

Now add the overflow problem: context windows and reasoning traces blow up the KV cache.

When KV cache can’t live comfortably on-device, systems start leaning on host memory tiers. One concrete industry signal: vLLM has explicitly discussed CPU‑memory KV cache offloading as a lever—offloading to CPU DRAM and optimizing host↔device transfer to keep throughput up.

That’s the “GPU engine, CPU fuel line” metaphor made literal: when GPU memory becomes the scarce tier, the CPU memory subsystem becomes the staging ground that decides whether the GPU is fed or starved.

And this is where the missing 2026 keyword belongs in the story:

CXL (Compute Express Link) is the industry’s practical answer to “stranded memory.” It’s how hyperscalers plan to pool and expand memory beyond what’s soldered to a single board, so orchestration workloads (and huge contexts) don’t get hard-capped by local DRAM slots.

The punchline is that agent economics make memory fungibility valuable. CXL is how you buy fungibility.

Autonomy creates bureaucracy. Bureaucracy creates CPU load.

The moment you let an AI system do anything “real”—

execute code, browse the web, access internal tools, write to a repo, touch production data—

you wrap it in isolation and policy: containers or microVMs, network controls, resource monitoring, audit logs, guardrails, and permission layers.

That overhead is not a rounding error. It’s the operational state machine around “doing work safely.”

AWS ($AMZN) is pretty direct about what it takes to run code interpreter-like agent workloads securely: you need managed environments, isolation boundaries, and a bunch of infrastructure around execution—not just a model endpoint.

And that overhead is mostly CPU-side orchestration. The GPU doesn’t run your audit trail. The GPU doesn’t enforce your egress policy. The GPU doesn’t spin up your sandbox.

Agents don’t remove enterprise bureaucracy. They automate it.

So the bureaucracy loop starts running at machine speed.

The networking tax: east‑west traffic becomes the silent limiter

There’s another bottleneck you can’t dodge once you go rack-scale: east‑west traffic inside the data center.

An agent “thinking” in production looks like this:

Query a vector DB → call a tool → update a log → fetch another document → run a verifier → write back state → repeat.

That’s a lot of internal movement, not just “compute.”

Which is why DPUs, SmartNICs, and high-end NICs show up as first-class orchestration components. In Rubin-era designs, you can see NVIDIA bundling BlueField DPUs and ConnectX networking directly into the platform story.

And it’s not just $NVDA. Broadcom ($AVGO) has been explicit about AI data-center “traffic controller” silicon and is pushing higher-performance Ethernet-scale solutions aimed at AI workloads.

So when we say “CPUs are the orchestration layer,” we should be honest: it’s really CPU + NIC + DPU as the orchestration layer. The CPU increasingly offloads parts of the networking “tax” to the DPU so the whole rack doesn’t drown in packets and policy checks.

Where RL joins in: agents become policies, not prompts—and that multiplies infrastructure demand

Once agents become the interface, reinforcement learning (RL) becomes the factory that turns them into workers.

And RL doesn’t just “make the model better.” It changes the workload shape:

It introduces exploration, multiple rollouts, evaluation, reward computation, and selection among alternatives. That means more attempts per task, not fewer.

DeepSeek’s R1 work is a concrete example people cite here: it reports that reasoning behaviors can be incentivized with RL, with emergent patterns like self-verification and self-reflection—exactly the behaviors that expand the inference graph into longer, more iterative loops.

And in agentic RL, “environment steps” aren’t toy gridworld frames. They can be headless browsers, containerized code runners, staging databases, API sandboxes, or CI pipelines.

That’s where CPUs get hammered: environment orchestration, reward evaluation, parallel sandboxes, state resets, trajectory storage—this is CPU/I/O scaling pressure.

RL is a multiplier on the orchestration thesis.

The shortage signal isn’t “empty shelves.” It’s price steps, allocation warfare, and lead times.

If you’re looking for a 2026 shortage, don’t imagine a consumer GPU shelf in 2021. Modern shortages show up as:

selective price hikes,

prioritization of higher-margin SKUs,

supply reserved for hyperscalers and anchor customers,

lead times that quietly stretch until they become planning constraints.

On the client side, reporting in late 2025 pointed to price increases on older Intel CPUs (notably Raptor Lake-era parts) on the order of ~10%+—with some markets seeing larger moves.

On the server side, Intel ($INTC) has publicly discussed a CPU supply shortage impacting data center/server availability, with expectations that the tightest point would be in Q1 2026 and improvement would follow later in the year.

And the memory side is not quietly behaving like a commodity anymore either: Reuters has described dynamics where AI server memory demand is pushing pricing up materially, with tightness expected to ripple through the supply chain.

That’s what an oncoming structural crunch looks like early: not “no inventory,” but repricing + rationing.

Why 2026 is a collision year: demand shifts just as supply hits hard physical limits

The 2026 argument gets stronger when you frame it as a collision between:

a structural demand shift (agents + test-time compute + RL loops), and

a supply system already operating near limits.

On the supply side, multiple signals stack:

TSMC ($TSM; 2330.TW) leadership has described leading-edge capacity as “very, very tight,” with constraints extending into 2026.

Analysts cited in EE Times estimate that wafer demand at 5nm and below could exceed capacity by ~25–30% in 2026, implying persistent tightness at the nodes that matter most for flagship silicon.

Reuters reported TSMC guiding to 2026 capex of roughly $52–$56B with expectations of strong 2026 growth—important, but still not instant capacity (fabs don’t show up on quarterly timelines).

Now layer in the “this is how physical reality works” details:

ASML’s ($ASML) High‑NA EUV tools cost hundreds of millions of dollars per unit and ship in hundreds of crates; Reuters noted they’re expected to be used in commercial manufacturing starting 2026 or 2027.

In other words, even when the industry spends aggressively, the constraint is time.

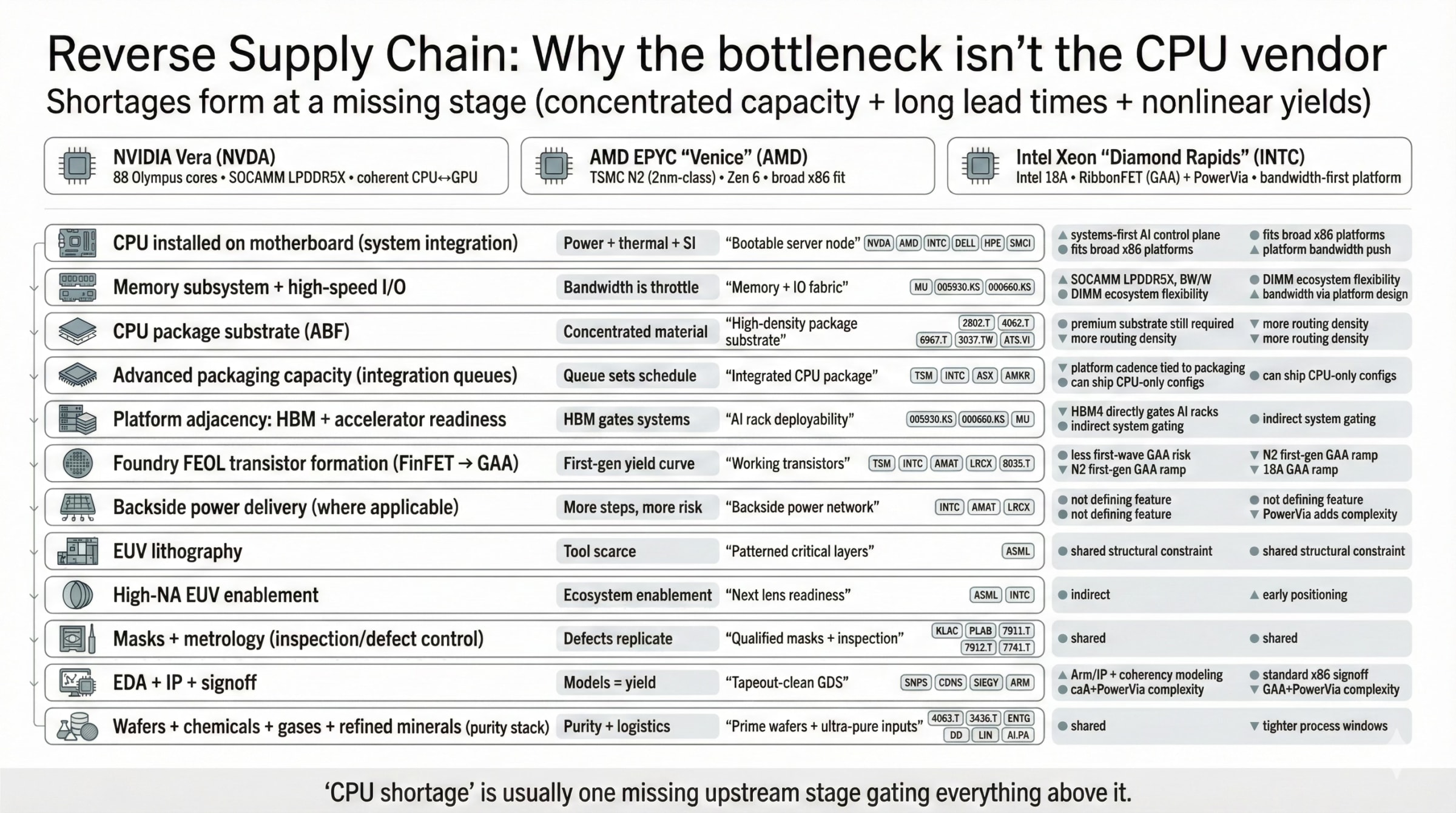

The reverse supply chain matters because the bottlenecks are not “the CPU vendor.” They’re the missing stage.

This is where your deep-dive framing really earns its keep. If you trace a finished server node backward, you quickly realize the choke points are specific stages where:

only a few suppliers dominate,

capacity takes years to expand,

yields make output non-linear,

and downstream assembly can’t proceed if one input is missing.

So let’s walk it backwards—more conversationally—but without losing the technical spine.

Stage 1: CPU installed on the motherboard (system integration)

This is where NVIDIA ($NVDA), AMD ($AMD), and Intel ($INTC) collide with the real constraints of OEMs and integrators like Dell ($DELL), HPE ($HPE), and Super Micro ($SMCI). At 2026 power levels, the binding constraint is often not core count, but whether the platform can deliver stable power, remove heat, and keep I/O stable under continuous load. Vera is built around a systems-first narrative and is designed to behave like a control plane for AI factories. Venice is designed to slide into the broad x86 server ecosystem with minimal friction. Diamond Rapids signals a platform-level bandwidth push that increases board complexity and routing density.

Stage 2: Memory subsystem and high-speed I/O (the “library and highways”)

Agentic workloads do not just compute, they hold state and move it constantly. They pull context, call tools, write logs, store intermediate artifacts, and keep environments alive while the loop runs. Memory bandwidth and I/O stop being secondary specs and become the throttle. Vera’s differentiation is its LPDDR5X approach through SOCAMM-style designs, prioritizing bandwidth per watt and tight coupling to the GPU factory model. Venice stays anchored in conventional DIMM ecosystems for maximum platform flexibility. Diamond Rapids pushes toward more aggregate bandwidth through platform choices that increase routing and power delivery complexity. This is also where CXL becomes the practical survival mechanism for “stranded memory,” enabling pooled expansion as context windows and reasoning traces grow.

Stage 3: CPU package substrate (ABF)

This is the multilayer wiring structure under the chip that makes high-speed signaling and high-current power delivery possible. Even flawless silicon cannot ship without sufficient high-end substrate capacity. The concentration here is the entire story. Ajinomoto (2802.T) is widely cited as holding near-total share in the insulation film used for high-performance ABF substrates. Substrate manufacturers such as Ibiden (4062.T), Shinko (6967.T), Unimicron (3037.TW), and AT&S (ATS.VI) cannot route signals without that material. Differentiation shows up as pressure profiles. Vera may emphasize a more uniform control-plane design, but it still needs a premium substrate to sustain coherent high-bandwidth signaling. Venice and Diamond Rapids mechanically increase substrate layer counts and routing density as they scale memory channels and I/O.

Stage 4: Advanced packaging capacity (assembly and integration queues)

Packaging is not just “put the die in a box.” It is the integration of dies or tiles, tight thermals, warpage control, and high yield under complex constraints. Capacity here is shared infrastructure, which is why it becomes a schedule setter. Foundries and OSATs such as TSMC ($TSM), Intel ($INTC), ASE ($ASX), and Amkor ($AMKR) become arbiters of volume when demand spikes. The exposure differs. Vera’s value proposition is tightly coupled to the broader Rubin platform cadence, which means packaging queues that gate accelerators can indirectly gate Vera-based system shipments. Venice and Diamond Rapids retain more ability to ship into non-AI server configurations, which can soften the shock when packaging bottlenecks bind.

Stage 5: The platform adjacency bottleneck (HBM and accelerator readiness)

AI servers do not ship as CPUs alone. They ship as platforms that require accelerator memory stacks, and that makes HBM a system-level limiter. If HBM4 is constrained, racks do not deploy, regardless of CPU availability. This creates asymmetric exposure. Vera is most directly tied to HBM availability because the Rubin narrative depends on coherent CPU to GPU memory movement and rack-scale determinism. Venice and Diamond Rapids can ship outside this dependency chain, but for flagship AI clusters the accelerator complex still sets the deployment pace.

Stage 6: Foundry FEOL transistor formation (FinFET to GAA transition)

This is where the 2026 story turns into a yield ramp story. Venice is tied to TSMC’s first-generation GAA-class process direction. Diamond Rapids is tied to Intel’s 18A RibbonFET roadmap. Both face nonlinear output as learning curves mature. This is where a small yield wobble can become a big supply shock.

Stage 7: Backside power delivery (where applicable)

Backside power approaches separate power delivery from frontside signal routing and can improve performance per watt, but they add process complexity and yield risk. Intel’s 18A strategy is closely associated with this style of shift, which makes it a key part of Diamond Rapids’ manufacturing risk profile.

Stage 8: EUV lithography (printing the smallest patterns)

EUV throughput and uptime become structural constraints because they define how quickly critical layers can be patterned at scale. ASML ($ASML) sits at the center. The tools are scarce, expensive, and operationally delicate, which is why EUV capacity is never “just add money.”

Stage 9: High-NA EUV enablement (the next lens system)

High-NA reduces multi-patterning but introduces ecosystem readiness constraints and extreme tool scarcity. Early adoption dynamics matter here because tool positioning can influence successor-node readiness and competitiveness.

Stage 10: Masks and metrology (defect control and inspection)

As nodes shrink and complexity rises, defect detection and mask quality become gating. KLA ($KLAC) is central in inspection and metrology. Mask makers like Photronics ($PLAB) and Japanese incumbents such as Toppan (7911.T), Dai Nippon Printing (7912.T), and HOYA (7741.T) sit in the critical path when mask counts rise and defect tolerance collapses.

Stage 11: EDA, IP, and signoff models (blueprints and building-code approval)

At the GAA era, modeling accuracy is yield. EDA vendors Synopsys ($SNPS), Cadence ($CDNS), and Siemens (SIEGY) define tapeout confidence. IP ecosystems like Arm ($ARM) matter especially for Vera’s compatibility story and for any platform pushing new coherency and system-level integration.

Stage 12: Wafers, chemicals, gases, and refined minerals (the purity stack)

This is the “clean kitchen” layer that determines whether leading-edge manufacturing is even possible. Wafers from Shin-Etsu (4063.T) and SUMCO (3436.T), process materials from Entegris ($ENTG) and DuPont ($DD), and gases from Linde ($LIN) and Air Liquide (AI.PA) all become more sensitive inputs as the industry moves into first-generation GAA ramps.

The takeaway is simple. “CPU shortage” is rarely a single company failing to ship. It is a shared pipeline where one missing stage can gate everything above it. Shortages emerge in phases. Allocation shifts first, then lead times stretch, then cascades form when one constrained input blocks multiple downstream assemblies. In 2026, Vera, Venice, and Diamond Rapids do not just compete on architecture. They collide on shared chokepoints, and their exposure differs depending on how tightly each strategy is coupled to the broader AI platform stack.

The 2026 platform clash: integration vs flexibility

This is where the competitive narrative gets fun, because the strategy split is clean: